June 19, 20116 minutes

For some reason, the Base System Builder in EDK doesn’t support the XUPV5 board so when making an EDK project for the XUPV5 we have to select the ML505 board and modify the project settings later. If you have not yet created an EDK project, you should read the previous post Creating a project using the Base System Builder, and then continue from these instructions.

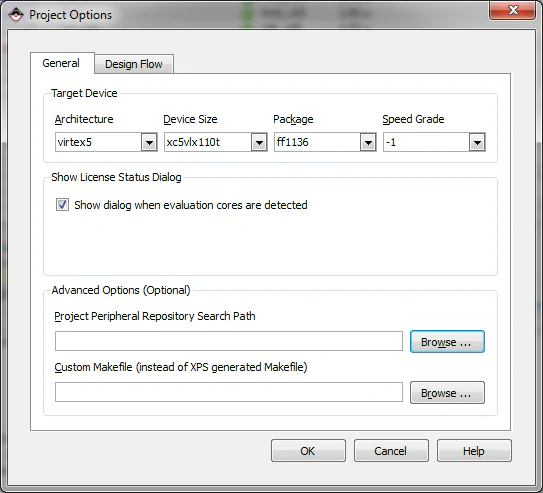

The ML505 is based on the Virtex-5 XC5VLX50T whereas the XUPV5 is based on the Virtex-5 XC5VLX110T, so the first thing we must do is change the target FPGA of the project.

We’re not finished yet so don’t get too excited and try building the bitstream. If you were to try to build the bitstream, you would come up with this error:

ERROR: Place:713 - IOB component "fpga_0_DDR2_SDRAM_DDR2_DQ_pin<13>" and IODELAY

component

"DDR2_SDRAM/DDR2_SDRAM/mpmc_core_0/gen_v5_ddr2_phy.mpmc_phy_if_0/u_phy_io_0/g

en_dq[13].u_iob_dq/u_idelay_dq" must be placed adjacent to each other into

the same I/O tile in order to route net

"DDR2_SDRAM/DDR2_SDRAM/mpmc_core_0/gen_v5_ddr2_phy.mpmc_phy_if_0/u_phy_io_0/g

en_dq[13].u_iob_dq/dq_in". The following issue has been detected:

Some of the logic associated with this structure is locked. This should cause

the rest of the logic to be locked.A problem was found at site IODELAY_X0Y56

where we must place IODELAY

DDR2_SDRAM/DDR2_SDRAM/mpmc_core_0/gen_v5_ddr2_phy.mpmc_phy_if_0/u_phy_io_0/ge

n_dq[13].u_iob_dq/u_idelay_dq in order to satisfy the relative placement

requirements of this logic. IODELAY

DDR2_SDRAM/DDR2_SDRAM/mpmc_core_0/gen_v5_ddr2_phy.mpmc_phy_if_0/u_phy_io_0/ge

n_dqs[0].u_iob_dqs/u_iodelay_dq_ce appears to already be placed there which

makes this design unplaceable.

ERROR: Pack:1654 - The timing-driven placement phase encountered an error.

ERROR: Xflow - Program map returned error code 2. Aborting flow execution...

make: *** [__xps/system_routed] Error 1

The reason for this error is that the design contains certain location constraints that are optimal for the Virtex-5 XC5VLX50T but not for the XC5VLX110T. We will have to modify the UCF file to use location constraints that are optimal for our FPGA.

The PCIe bridge peripheral that we included in the project has timing constraints in the project UCF file (system.ucf) but it also has some location constraints in its core specific UCF file (implementation/pcie_bridge_wrapper/pcie_bridge_wrapper.ucf). If you are curious, open this file and read the constraints inside.

The core specific UCF file is generated when you build the project and it is usually generated with constraints that are optimal for the target platform (ie. ML505 in our case). As the ML505 contains a smaller FPGA, the constraints are not optimal for the XUPV5 and we will have to override them by placing the same constraints (with different locations) into the project UCF file (system.ucf).

###############################################################################

# PCIe Bridge Constraints for XUPV5

###############################################################################

# BlockRAM placement

INST "pcie_bridge/*pcie_mim_wrapper_i/bram_tl_tx/generate_tdp2[1].ram_tdp2_inst" LOC = RAMB36_X3Y11;

INST "pcie_bridge/*pcie_mim_wrapper_i/bram_tl_rx/generate_tdp2[1].ram_tdp2_inst" LOC = RAMB36_X3Y9;

INST "pcie_bridge/*pcie_mim_wrapper_i/bram_tl_tx/generate_tdp2[0].ram_tdp2_inst" LOC = RAMB36_X3Y10;

INST "pcie_bridge/*pcie_mim_wrapper_i/bram_tl_rx/generate_tdp2[0].ram_tdp2_inst" LOC = RAMB36_X3Y8;

INST "pcie_bridge/*pcie_mim_wrapper_i/bram_retry/generate_sdp.ram_sdp_inst" LOC = RAMB36_X3Y7;

# Timing critical placements

INST "pcie_bridge/*tx_bridge/shift_pipe1" LOC = "SLICE_X59Y56";

INST "pcie_bridge/*arb_inst/completion_available" LOC = "SLICE_X58Y46";

INST "pcie_bridge/*management_interface/mgmt_rdata_d1_3" LOC = "SLICE_X59Y45";

The DDR2 memory controller peripheral is the other device with some critical location constraints that we will have to optimize for the XUPV5.

###############################################################################

# LOC placement of DQS-squelch related IDDR and IDELAY elements

# Each circuit can be located at any of the following locations:

# 1. Ununsed "N"-side of DQS diff pair I/O

# 2. DM data mask (output only, input side is free for use)

# 3. Any output-only site

###############################################################################

INST "*/gen_dqs[0].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y56";

INST "*/gen_dqs[0].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y56";

INST "*/gen_dqs[1].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y18";

INST "*/gen_dqs[1].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y18";

INST "*/gen_dqs[2].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y22";

INST "*/gen_dqs[2].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y22";

INST "*/gen_dqs[3].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y60";

INST "*/gen_dqs[3].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y60";

INST "*/gen_dqs[4].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y62";

INST "*/gen_dqs[4].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y62";

INST "*/gen_dqs[5].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y216";

INST "*/gen_dqs[5].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y216";

INST "*/gen_dqs[6].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y220";

INST "*/gen_dqs[6].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y220";

INST "*/gen_dqs[7].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y222";

INST "*/gen_dqs[7].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y222";

###############################################################################

# LOC and timing constraints for flop driving DQS CE enable signal

# from fabric logic. Even though the absolute delay on this path is

# calibrated out (when synchronizing this output to DQS), the delay

# should still be kept as low as possible to reduce post-calibration

# voltage/temp variations - these are roughly proportional to the

# absolute delay of the path

###############################################################################

INST "*/u_phy_calib_0/gen_gate[0].u_en_dqs_ff" LOC = SLICE_X0Y28;

INST "*/u_phy_calib_0/gen_gate[1].u_en_dqs_ff" LOC = SLICE_X0Y9;

INST "*/u_phy_calib_0/gen_gate[2].u_en_dqs_ff" LOC = SLICE_X0Y11;

INST "*/u_phy_calib_0/gen_gate[3].u_en_dqs_ff" LOC = SLICE_X0Y30;

INST "*/u_phy_calib_0/gen_gate[4].u_en_dqs_ff" LOC = SLICE_X0Y31;

INST "*/u_phy_calib_0/gen_gate[5].u_en_dqs_ff" LOC = SLICE_X0Y108;

INST "*/u_phy_calib_0/gen_gate[6].u_en_dqs_ff" LOC = SLICE_X0Y110;

INST "*/u_phy_calib_0/gen_gate[7].u_en_dqs_ff" LOC = SLICE_X0Y111;

###############################################################################

# LOC placement of DQS-squelch related IDDR and IDELAY elements

# Each circuit can be located at any of the following locations:

# 1. Ununsed "N"-side of DQS diff pair I/O

# 2. DM data mask (output only, input side is free for use)

# 3. Any output-only site

###############################################################################

INST "*/gen_dqs[0].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y96";

INST "*/gen_dqs[0].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y96";

INST "*/gen_dqs[1].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y58";

INST "*/gen_dqs[1].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y58";

INST "*/gen_dqs[2].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y62";

INST "*/gen_dqs[2].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y62";

INST "*/gen_dqs[3].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y100";

INST "*/gen_dqs[3].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y100";

INST "*/gen_dqs[4].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y102";

INST "*/gen_dqs[4].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y102";

INST "*/gen_dqs[5].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y256";

INST "*/gen_dqs[5].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y256";

INST "*/gen_dqs[6].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y260";

INST "*/gen_dqs[6].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y260";

INST "*/gen_dqs[7].u_iob_dqs/u_iddr_dq_ce" LOC = "ILOGIC_X0Y262";

INST "*/gen_dqs[7].u_iob_dqs/u_iodelay_dq_ce" LOC = "IODELAY_X0Y262";

INST "DDR2_SDRAM/DDR2_SDRAM/gen_no_iodelay_grp.gen_instantiate_idelayctrls[1].idelayctrl0" LOC = IDELAYCTRL_X0Y2;

INST "DDR2_SDRAM/DDR2_SDRAM/gen_no_iodelay_grp.gen_instantiate_idelayctrls[0].idelayctrl0" LOC = IDELAYCTRL_X0Y6;

INST "DDR2_SDRAM/DDR2_SDRAM/gen_no_iodelay_grp.gen_instantiate_idelayctrls[2].idelayctrl0" LOC = IDELAYCTRL_X0Y1;

###############################################################################

# LOC and timing constraints for flop driving DQS CE enable signal

# from fabric logic. Even though the absolute delay on this path is

# calibrated out (when synchronizing this output to DQS), the delay

# should still be kept as low as possible to reduce post-calibration

# voltage/temp variations - these are roughly proportional to the

# absolute delay of the path

###############################################################################

INST "*/u_phy_calib_0/gen_gate[0].u_en_dqs_ff" LOC = SLICE_X0Y48;

INST "*/u_phy_calib_0/gen_gate[1].u_en_dqs_ff" LOC = SLICE_X0Y29;

INST "*/u_phy_calib_0/gen_gate[2].u_en_dqs_ff" LOC = SLICE_X0Y31;

INST "*/u_phy_calib_0/gen_gate[3].u_en_dqs_ff" LOC = SLICE_X0Y50;

INST "*/u_phy_calib_0/gen_gate[4].u_en_dqs_ff" LOC = SLICE_X0Y51;

INST "*/u_phy_calib_0/gen_gate[5].u_en_dqs_ff" LOC = SLICE_X0Y128;

INST "*/u_phy_calib_0/gen_gate[6].u_en_dqs_ff" LOC = SLICE_X0Y130;

INST "*/u_phy_calib_0/gen_gate[7].u_en_dqs_ff" LOC = SLICE_X0Y131;

Now you are ready to build the project and if you have done everything right, you should not have any errors.

Checking platform address map ...

Initializing Memory...

Running Data2Mem with the following command:

data2mem -bm "implementation/system_bd" -p xc5vlx110tff1136-1 -bt

"implementation/system.bit" -bd "bootloops/microblaze_0.elf" tag microblaze_0

-o b implementation/download.bit

Memory Initialization completed successfully.

Done!

You can download the project files as a compressed zip file here: base-system-xupv5-edk13-1.zip