Measuring NVMe SSD read/write speeds on the ZCU106 with FPGA Drive FMC under PetaLinux

December 2, 20196 minutes

IntelliProp demonstrates 3200 MB/s read speeds with their NVMe IP on an Intel Arria 10 and FPGA Drive

February 26, 20181 minute

Video demo of IntelliProp NVMe IP on the KCU105 achieving nearly 2 GB/s read speeds via FPGA Drive FMC

January 31, 20171 minute

Video showing how to physically connect an M.2 SSD to the FPGA Drive FMC adapter

January 28, 20171 minute

IntelliProp tests their NVMe Host Accelerator IP on FPGA Drive achieving up to 2000 MB/s read speeds

October 23, 20162 minutes

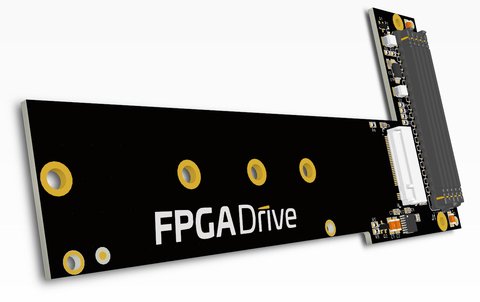

Announcing availability of the FPGA Drive PCIe and FMC adapters for connecting M.2 SSDs to FPGAs

August 17, 20162 minutes

Benchmarking NVMe SSD read/write speeds on KC705 and PicoZed running PetaLinux

July 2, 20164 minutes

Introducing the FPGA Drive FMC for connecting NVMe PCIe SSDs to FPGAs without expensive IP cores.

July 1, 20163 minutes

First look at the FPGA Drive FMC version with HPC connector and support for 4-lane PCIe M.2 SSDs.

June 8, 20161 minute

Tutorial on connecting an NVMe SSD to an FPGA and accessing it from PetaLinux using FPGA Drive.

April 15, 201614 minutes