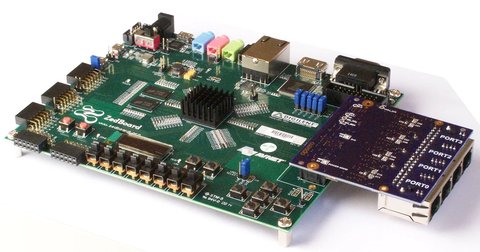

Building a custom PetaLinux image for the ZedBoard with four extra Ethernet ports via Ethernet FMC.

May 4, 20169 minutes

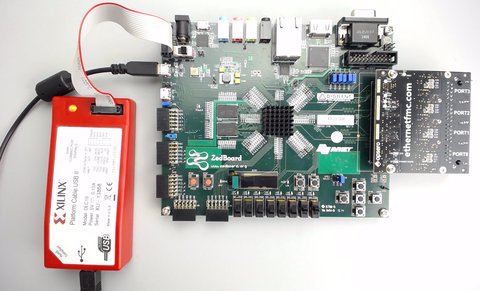

Testing a multi-port Ethernet design by running a lwIP echo server on the ZedBoard with Ethernet FMC.

January 5, 201611 minutes

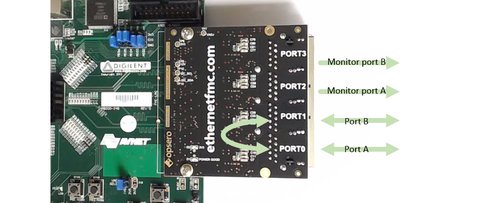

Designing a transparent Ethernet pass-through in Vivado as the foundation for an FPGA network tap.

December 29, 20157 minutes

Announcing a new LPC FMC with four Marvell Gigabit Ethernet PHYs for FPGA networking applications.

October 13, 20141 minute

Introducing two new SERDES FMC boards that add external multi-gigabit transceivers to the ZedBoard.

September 5, 20142 minutes

Side-by-side comparison of available Zynq-7000 development boards by features and price

March 4, 20148 minutes